> edyさんのソースコードを拝借。

実験してみたところ、CY8C27443-24PXI で、100MHz迄動作する事を確認した。

流石に125MHzでは、とんでもない大きな数字が表示されてNGだった。

但し、実験なので内蔵発振をクロックにしており、実用不適。

マトモに使うには、外部から正確なクロックを注入してやる必要がある。

P.S.

その後、外部クロックとして12.8MHz TCXO を注入してみたが、内部クロックでも、外部クロックでも、65,536Hz(64kHz)の飛びが見られた。注入クロックと被測定信号を同一にした場合には、飛びは発生しない。非同期でcounterを動作させる点に少々無理がある様だ。

> 割り込みを使わない方式に変更。

16bit counterを2つカスケード接続した。

やはり、64kHzの飛びが発生する。

内部クロックでは精度が悪いので、外部クロックに切替。

(割り込み無し版)

P.S.

P1[4]を High Z Analog → High Z に変更要。

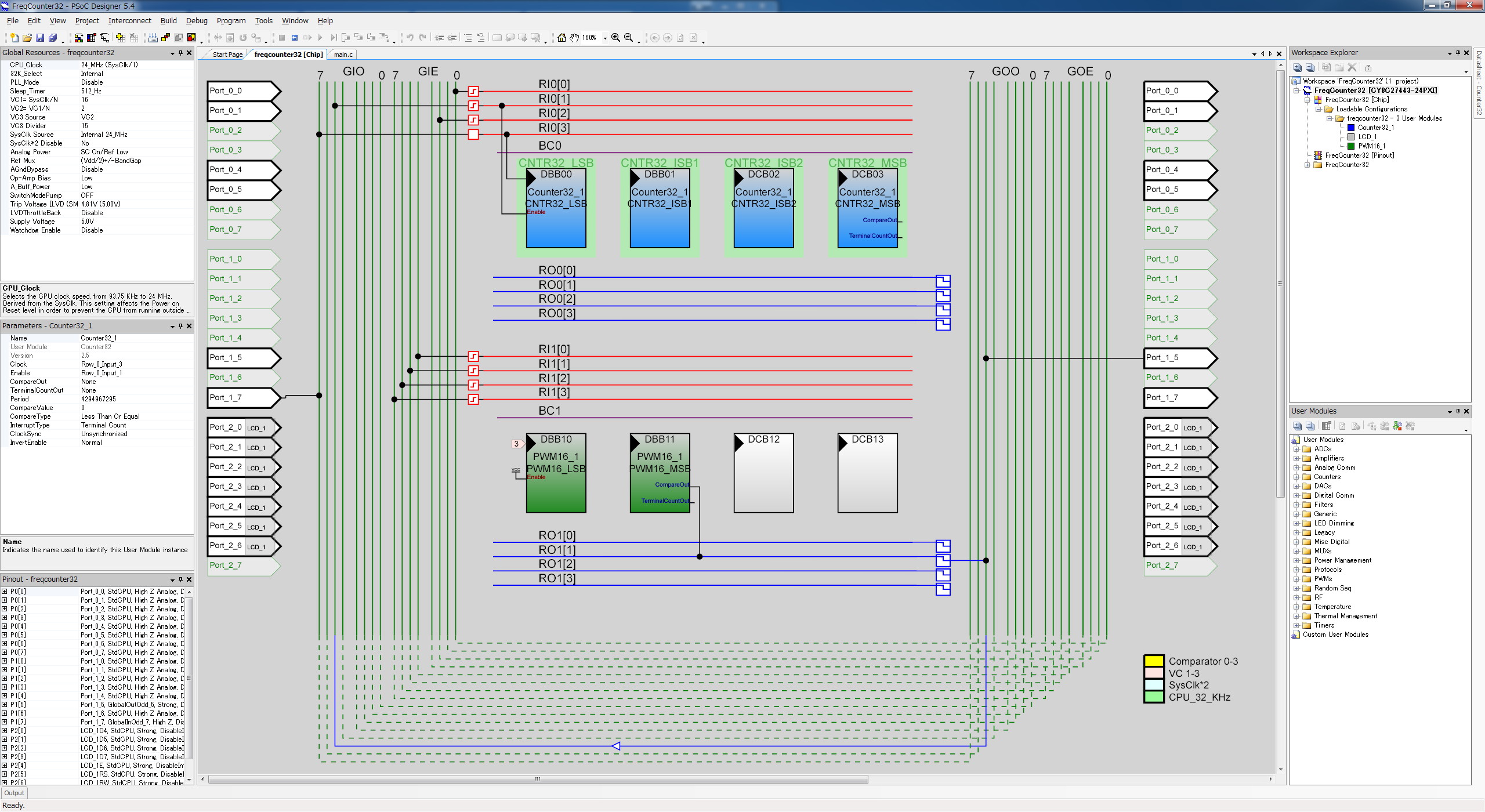

回路図

24MHzの発振器の手持ちがなかったので、26MHzで代用した。

一応問題なく動作している。(除:飛び問題)

CY8C27443では、32bit counterに外部信号をカウントさせる事ができないので、16bit counterを2段カスケードにしたのだが、時折MSB側のcounterが1つミスカウントして、表示が65,535Hz跳ね上がるという問題が発生した。

そこで、2つの16bit counterを、同じ列に配置して、LSB側の出力をMSB側に直に渡す様に改良してみたのだが。

結果は、余り改善されておらず、やはり64kHzの跳ね上がりが発生する。

外部クロックをTCXO 12.8MHzに変更。

手持ちのTCXOは、出力が弱いので増幅要。

VR1はdutyの調節。余りdutyが悪いと、PSoCはヘソを曲げる様だ。

更に、schmitt tgiggerで波形整形。

アイコン

注入する外部クロックを、被計測信号とする限りにおいては、64kHzのミスカウントは全く発生しないので、要因は、注入するクロックの質、または、counterの非同期耐性にあるのであろう。

64kHz飛ぶならば、という事で、counterを16bit2段を止めて、24bit+8bit にしてみた。これならば、16MHz飛びになるので、発生確率を抑えられるだろうと思ったのだが、結果は逆で、16MHz,64kHz,256Hzの3種の飛びが現れる様になった。よく観察すると、他にも2MHz飛びとかも存在している様で、最悪。

更に、24bit counterは16it counterより性能が悪い様で、16bit counterの時に測定できていた100MHzが、24bit counterでは測定できなくなった。60MHzなら、24bit counterでも測定できる。内部24MHzクロックの時も同様なので、外部クロックが12.8MHzである事のせいではない様だ。

24bit counter用の3 byte読出しは、pointerになるので、プログラムの変更が必要。

64kHz飛びに対処する為、割り込み方式、且つ、8bit counterに変えてみた。

P.S.

64kHz飛びは無くなったが、256Hz飛びは発生する。

100MHzは測定できなくなる、88MHz台が表示される。

60MHzは問題無く(除:256Hz飛び)測定できる。

プログラムの改修は、8bit counter対応のみ。

P.S.

100MHzを測定しようとすると、61クロックに1回割込みが発生する訳だから苦しいよね。

88MHz台が表示されるという事は、割込みルーチンで69クロック程消費しているという事だろうか。

> CY8C27443では、32bit counterに外部信号をカウントさせる事ができない

というのは間違いで、32bit counterの4セルを横1列に並べれば解決する。

但し、PWM16とは別の段になるので、グルっとゲート信号を回さねばならない。

PSoC内部で引き回すと、結構回り込みの元な様だ。

被測定信号が矩形波なら、正常に動作する様だ。

被測定信号が矩形波以外の場合は、過剰にカウントする事が多い。

> 32bit counterの4セルを横1列に並べれば解決する。

32bit counterなので、数字の上では4GHz迄カウントできる。

PSoCのハードウェアが4GHzに対応するとは思えないので、割込は廃した。

> > 32bit counterの4セルを横1列に並べれば解決する。

回路図

ゲート信号の引き回しがPSoC内部

> PSoC内部で引き回すと、結構回り込みの元な様だ。

PSoC外部で引き回す様に変更。

ソースコードは変わらない。

> > PSoC内部で引き回すと、結構回り込みの元な様だ。

>

> PSoC外部で引き回す様に変更。

100MHzは計測できる様だ。

但し、矩形波に限る。

他の波形では、表示数値の変動が激しい。

真面目にノイズ対策する必要がありそう。